Processor P-States i C-States

Procesory Intel obsługują wiele technologii w celu optymalizacji zapotrzebowania na energię. W tym artykule przedstawiamy przegląd stanów P-State (optymalizacja napięcia i częstotliwości procesora podczas pracy) oraz stanów C-State (optymalizacja zużycia energii, gdy rdzeń nie posiada instrukcji do wykonania). Informacje na temat wyłączania tych funkcji można znaleźć w artykule Jak wyłączyć CPU Power Saving Management w BIOS-ie.

P-States

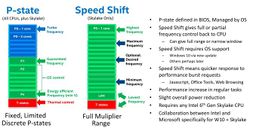

Podczas wykonywania kodu, system operacyjny i procesor mogą zoptymalizować zużycie energii przez różne stany P (Performance States). W zależności od potrzeby, procesor pracuje w różnych częstotliwościach. P0 jest najwyższą częstotliwością (z najwyższym napięciem).

W przypadku procesorów Intel do architektury Haswell/Broadwell włącznie, żądana częstotliwość (a tym samym napięcie) jest określana przez system operacyjny za pośrednictwem wpisywania żądanych wartości do specjalnych rejestrów procesora.[1][2]

Począwszy od architektury Skylake, system operacyjny może przekazać kontrolę nad stanami P procesorowi (Speed Shift Technology, Hardware P-States).[3] W architekturze Kaby Lake, funkcje te zostały jeszcze bardziej zoptymalizowane.[4]

C-States

W przeciwieństwie do stanów P, których celem jest optymalizacja zużycia energii podczas wykonywania kodu, stany C służą do optymalizacji lub zmniejszenia zużycia energii w trybie bezczynności (gdy kod nie jest wykonywany).

Typowe stany C to:[5]

- C0 – Active Mode: Code is executed, in this state the P-States (see above) are also relevant.

- C1 – Auto Halt

- C1E – Auto halt, low frequency, low voltage

- C2 – Temporary state before C3. Memory path open

- C3 – L1/L2 caches flush, clocks off

- C6 – Save core states before shutdown and PLL off

- C7 – C6 + LLC may be flushed

- C8 – C7 + LLC must be flushed

Stany C można podzielić na Core C-States (CC-States), Package C-States (PC-States) i Logical C-State. W większości przypadków system operacyjny wyznacza określony stan C dla rdzenia poprzez wykonanie polecenia MWAIT.[6]

Odnośniki

- ↑ Intel Xeon Processor E3-1200 v3 Product Family Datasheet – Volume 1 of 2 4.2.1 Enhanced Intel SpeedStep Technology Key Features: [...] Multiple frequency and voltage points for optimal performance and power efficiency. These operating points are known as P-states. [...] Frequency selection is software controlled by writing to processor MSRs. [...] All active processor cores share the same frequency and voltage. In a multicore processor, the highest frequency P-state requested among all active cores is selected.

- ↑ What exactly is a P-state? (Pt. 1)

- ↑ Intel’s 6th Gen Skylake Unwrapped – CPU Microarchitecture, Gen9 Graphics Core and Speed Shift Hardware P-State (wccftech.com, 18.08.2015)

- ↑ Intel Kaby Lake: 14nm+ und optimiertes Speed Shift steigern Performance (TKmag, 10.03.2017)

- ↑ Intel Xeon Processor E3-1200 v5 Product Family Datasheet - Volume 1 of 2 Chapter 4 Power Management

- ↑ C-states, C-states and even more C-states (software.intel.com, 27.03.2008)

Dodatkowe informacje

- Energy-Efficient Platforms – Considerations for Application Software and Services (www.intel.com, März 2011)

- C-States, P-States, S-States - Energieverwaltung erklärt (www.technikaffe.de, 23.10.2013)

- What are the CPU c-states? How to check and monitor the CPU c-state usage in Linux per CPU and core? (golinuxhub.com, 08.06.2018)

Autor: Werner Fischer