Prozessor P-States und C-States

Intel Prozessoren unterstützen mehrere Technologien zur Optimierung des Energiebedarfs. In diesem Artikel geben wir einen Überblick über P-States (Optimierung der Spannung und CPU-Frequenz im Betrieb) und C-States (Optimierung des Energiebedarfs wenn ein Core keine Instruktionen auszuführen hat). Informationen zum Deaktivieren dieser Funktionen finden Sie im Artikel CPU Power Saving Management im BIOS deaktivieren.

P-States

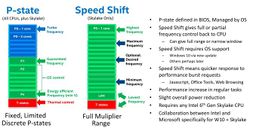

Während der Ausführung von Code können Betriebssystem und CPU den Energiebedarf durch unterschiedliche P-States (Performance States) optimieren. Je nach Bedarf wird eine CPU mit unterschiedlichen Frequenzen betrieben. P0 ist dabei die höchste Frequenz (mit der höchsten Spannung).

Bei Intel Prozessoren bis inkl. der Haswell/Broadwell-Architektur wird die gewünschte Frequenz (und damit die Spannung) durch das Betriebssystem vorgegeben, indem es die gewünschten Werte in spezielle Prozessor Register schreibt.[1][2]

Ab der Skylake Architektur kann das Betriebssystem die Steuerung der P-States der CPU überlassen (Speed Shift Technology, Hardware P-States).[3] Mit Kaby Lake wurden diese Funktionen weiter optimiert.[4]

C-States

Im Gegensatz zu den P-States, welche die Optimierung des Stromverbrauchs bei der Ausführung von Code zum Ziel haben, dienen C-States zur Optimierung bzw. Verringerung des Stromverbrauchs im Idle-Modus (also dann, wenn kein Code ausgeführt wird).

Typische C-States sind:[5]

- C0 – Active Mode: Code wird ausgeführt, in diesem Zustand sind auch die P-States (siehe oben) relevant.

- C1 – Auto Halt

- C1E – Auto halt, low frequency, low voltage

- C2 – Temporary state before C3. Memory path open

- C3 – L1/L2 caches flush, clocks off

- C6 – Save core states before shutdown and PLL off

- C7 – C6 + LLC may be flushed

- C8 – C7 + LLC must be flushed

C-States können nach Core C-States (CC-States), Package C-States (PC-States) und Logical C-State unterschieden werden. In den meisten Fällen setzt das Betriebssystem einen bestimmten C-State für einen Core, indem es den MWAIT Befehl ausführt.[6]

Einzelnachweise

- ↑ Intel Xeon Processor E3-1200 v3 Product Family Datasheet – Volume 1 of 2 4.2.1 Enhanced Intel SpeedStep Technology Key Features: [...] Multiple frequency and voltage points for optimal performance and power efficiency. These operating points are known as P-states. [...] Frequency selection is software controlled by writing to processor MSRs. [...] All active processor cores share the same frequency and voltage. In a multicore processor, the highest frequency P-state requested among all active cores is selected.

- ↑ What exactly is a P-state? (Pt. 1)

- ↑ Intel’s 6th Gen Skylake Unwrapped – CPU Microarchitecture, Gen9 Graphics Core and Speed Shift Hardware P-State (wccftech.com, 18.08.2015)

- ↑ Intel Kaby Lake: 14nm+ und optimiertes Speed Shift steigern Performance (TKmag, 10.03.2017)

- ↑ Intel Xeon Processor E3-1200 v5 Product Family Datasheet - Volume 1 of 2 Chapter 4 Power Management

- ↑ C-states, C-states and even more C-states (software.intel.com, 27.03.2008)

Weitere Informationen

- Energy-Efficient Platforms – Considerations for Application Software and Services (www.intel.com, März 2011)

- C-States, P-States, S-States - Energieverwaltung erklärt (www.technikaffe.de, 23.10.2013)

- What are the CPU c-states? How to check and monitor the CPU c-state usage in Linux per CPU and core? (golinuxhub.com, 08.06.2018)

|

Autor: Werner Fischer Werner Fischer arbeitet im Product Management Team von Thomas-Krenn. Er evaluiert dabei neueste Technologien und teilt sein Wissen in Fachartikeln, bei Konferenzen und im Thomas-Krenn Wiki. Bereits 2005 - ein Jahr nach seinem Abschluss des Studiums zu Computer- und Mediensicherheit an der FH Hagenberg - heuerte er beim bayerischen Server-Hersteller an. Als Öffi-Fan nutzt er gerne Bus & Bahn und genießt seinen morgendlichen Spaziergang ins Büro. |