ATP Premium RAM

Inside each DDR SDRAM module are memory chips that consist of numerous integrated circuits (ICs), which must operate reliably over long periods of time. This article shows the additional quality characteristics of ATP Premium RAM Modules.

Memory module features

| Traditional memory | Traditional memory (Server Grade) |

ATP Premium RAM (Enterprise Grade) |

ATP RAM Wide Temp (Industrial Grade) | ||

|---|---|---|---|---|---|

| PCB (Printed Circuit Board) | PCB Layer | varies | 6-10 Layer | ||

| Gold Finger | <= 10µ" | 30µ" | |||

| Test procedure | System test | POT (Power On Test) | 100% on board Testing | ||

| Module function test | ATE | ATE & Module-Level TDBI | |||

| RMA process | Repair or replacement | ✔ | |||

| Error analysis on module level | ✔ | ||||

| 8D Report[1] | ✔ | ||||

| DDPM Management (Defective Parts per Million) |

Defined quality PPM | <3500ppm | <2000ppm | <500ppm | |

| DPM Monitoring | Monitoring of DPM errors in the field | ||||

| Product change (PCN) | LTB (Last Time Buy) | varies | 1 Month | 1 Quarter | |

| LTS (Last Time Ship) | varies | 1 additional Month (NCNR PO)[2] | 1 additional Quarter (NCNR PO) | ||

| Manufacturer warranty | Warranty period | varies | 2 or 3 years | 10 years | |

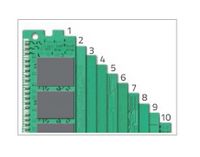

PCB Features

The thickness of the gold fingers as well as the number of layers of the PCB have an influence on the quality of a RAM module.

Goldfinger

Gold fingers are the gold-plated edge connector contacts on the DRAM printed circuit board (PCB) assembly. They are named this way because they are long and narrow like fingers. They are gold-plated to protect the PCB from wear and tear. To ensure the quality of signal transmission between the connector and the ATP DRAM module, ATP uses a gold finger coating with a thickness of 30µ".

PCB Layer

In addition, the board itself consists of 6-10 layers of printed circuit board (PCB) assemblies, which ensure better signal quality as well as durability of the module.

Test procedures

Automatic Testing Equipment (ATE)

Functional testing with Automatic Testing Equipment (ATE) detects component defects and structural defects associated with the DIMM assembly and filters out modules with marginal timing and signal integrity (SI) sensitivities. ATE provides electrical test patterns with various parameter settings such as marginal voltage, signal frequency, clock, command timing and data timing under continuous thermal cycling. The ATE test system can locate individual defective ICs or DRAM PC boards, providing a more efficient method of failure analysis for both new product development and mass production.

Translated with www.DeepL.com/Translator (free version)[3]

Test During Burn-In (TDBI)

The ATP-TDBI system tests DRAM modules at extremely high/low temperatures, at high/low voltages, and with patterns. The system consists of:

- The miniature chamber, where temperature cycling is limited only to the module under test so as not to thermally stress the other test systems. This minimizes the failure of other test components, such as the motherboards. In conventional large thermal chambers, non-DRAM related test component failures are constant as the entire system is thermally stressed.

- Module riser adapters from the motherboard, allowing easy insertion of modules in production quantities.

- Multiple temperature sensors that regulate temperature profiles and operate over a wide test temperature range from -40°C to 95°C.

Accelerated testing techniques such as TDBI reduce failure rates and extend product life by ensuring only robust DRAM chips are on the module. Even a defect as small as 0.01% on a 99.99% effective device can increase module-level failure rates and lead to real-world failure. TDBI detects and segregates up to 0.01% defects to ensure DRAM module reliability.[3]

Further Information

- DRAM Stress to Fail Test for Maximum Reliability (www.atpinc.com/blog, 16.12.2020)

- ATP’s Fastest “Industrial Only” DDR4 Memory Modules Meet the Need for Speed (www.atpinc.com/blog, 01.04.2020)

- ATP’s Fast, Low-Power “Industrial Only” DDR4-3200 DRAM Solutions Deliver Memory Boost to AMD EPYC™ and 2nd Generation Intel® Xeon® Scalable Processors (www.atpinc.com, Pressrelease 02.03.2020)

References

- ↑ Eight disciplines problem solving (en.wikipedia.org)

- ↑ NCNR PO: non-cancelable, non-returnable product order

- ↑ 3.0 3.1 Stringent Tests from ICs to Modules Ensure DRAM Reliability (www.atpinc.com/blog, 25.10.2018)

|

Author: Werner Fischer Werner Fischer, working in the Knowledge Transfer team at Thomas-Krenn, completed his studies of Computer and Media Security at FH Hagenberg in Austria. He is a regular speaker at many conferences like LinuxTag, OSMC, OSDC, LinuxCon, and author for various IT magazines. In his spare time he enjoys playing the piano and training for a good result at the annual Linz marathon relay.

|