POWER8

| Uwaga: Prosimy zwrócić uwagę, że ten artykuł / kategoria nie jest już aktualizowana, gdyż odnosi się do starszych komponentów oprogramowania / sprzętu. Ta strona jest nadal dostępna jedynie w celach informacyjnych. |

|---|

Procesory POWER8 są wykorzystywane między innymi w serwerach OpenPOWER. W tym artykule przedstawiamy niektóre z właściwości tych procesorów, takie jak liczba rdzeni lub wątków, jak i informacje o wielkości pamięci cache i właściwości zintegrowanych "Accelerators".

Procesory POWER8

Procesory POWER8 są dostępne z 4, 6, 8, 10 lub 12 rdzeniami.[1] Następująca tabela przedstawia przykładowe procesory POWER8 z 8 i 10 rdzeniami:[2][3][4]

| Rdzenie | Maks. threads (bei SMT=8) | Częstotliwość (nominalna) | Częstotliwość (turbo) | TDP (nominalne) | Part Number |

|---|---|---|---|---|---|

| 8 | 64 | 2.328 GHz | 3.026 GHz | 130 W | 00UL867 |

| 8 | 64 | 3.325 GHz | 3.857 GHz | 190 W | 00UL866 |

| 10 | 80 | 2.095 GHz | 2.827 GHz | 130 W | 00UL865 |

| 10 | 80 | 2.926 GHz | 3.492 GHz | 190 W | 00UL864 |

Przykładowy wynik z lscpu

W poniższym przykładzie jest przedstawiony wynik komendy lscpu wykonanej na serwerze 2U OpenPOWER single CPU RP2112. Ten serwer jest wyposażony w procesor z 8 rdzeniami i TDP 190W (Part Number 00UL866):

tk@ubuntu-16-04:~$ sudo lscpu Architecture: ppc64le Byte Order: Little Endian CPU(s): 64 On-line CPU(s) list: 0-63 Thread(s) per core: 8 Core(s) per socket: 8 Socket(s): 1 NUMA node(s): 1 Model: 2.0 (pvr 004d 0200) Model name: POWER8 (raw), altivec supported CPU max MHz: 3857.0000 CPU min MHz: 2061.0000 L1d cache: 64K L1i cache: 32K L2 cache: 512K L3 cache: 8192K NUMA node0 CPU(s): 0-63

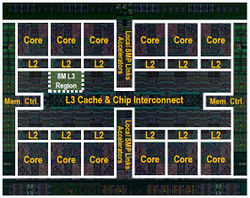

Cache procesorów POWER8

Systemy bazujące na architekturze POWER8 rozszerzają hierarchie cache'a o jedną warstwę, cache L4. Jest on zintegrowany w chipie Memory Buffer Chip (Centaur) na płycie głównej. Cache ten zawiera:[5]

| Cache | Wielkość | Przepustowość | Całkowita wielkość w 8-rdzeniowym procesorze |

|---|---|---|---|

| L1 Instruction | 32 KB / Core | 256 KB | |

| L1 Data | 64 KB / Core | Four 16 B reads or one 16 B writes per cycle | 512 KB |

| L2 | 512 KB / Core | 64 B reads und 16 B writes per cycle | 4 MB |

| L3 | 8 MB / Core | 32 B reads und 32 B writes per cycle | 64 MB |

| L4 | 16MB / Centaur Chip | np. 64 MB w 4 chipach Centaur |

Szczegółowe informacje o cache'u i podsystemie pamięci w procesorach POWER8 znajdują się na stronie researchgate.net.[6]

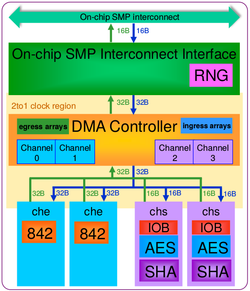

POWER8 CPU Accelerators

Procesory POWER8 zawierają tak zwane On Chip Accelerators (na CPU) i In Core Accelerators (na rdzeń). Umożliwiają one przyspieszenie określonych zadań, np. sprzętowego szyfrowania lub kompresji.[7]

On Chip Accelerators

Tak zwane Second generation Nest Accelerator complex (NX), część procesora POWER8 oferuje następujące funkcje:

- Szyfrowanie: Encryption Engine for Symetric Crypto

- Kompresja: Two 842 compression / decompression engines

- Generator liczb losowych: Random Number Generator

NX umożliwia każdemu rdzeniowi procesora dostęp do całej pamięci systemu POWER8. Dostęp odbywa się poprzez system Linuksa, który jest uruchomiony bezpośrednio na systemie POWER8, nie jest wirtualizowany w KVMie.

In Core Accelerators

Następujący akcelerator jest zintegrowanym w każdym rdzeniu:

- Symetric Crytpo

Może on również zostać wykorzystany bezpośrednio z systemu gościa (np. KVM).

OpenSSL od wersji 1.0.2 korzysta bezpośrednio z tego akceleratora.[8] Następujące dystrybucje Linuksa zawierają OpenSSL w wersji >= 1.0.2, a tym samym wspierają architekturę POWER8:

Odnośniki

- ↑ POWER8 (en.wikipedia.org)

- ↑ TYAN CPU Support - POWER8 (www.tyan.com)

- ↑ POWER8 CPUs (www.crowdsupply.com)

- ↑ GT75-BP012 FRU Parts Table (www.tyan.com)

- ↑ S812LC Technical Overview and Introduction Table 1-5 POWER8 cache hierarchy (www.redbooks.ibm.com)

- ↑ The cache and memory subsystems of the IBM POWER8 processor (www.researchgate.net, Article in IBM Journal of Research and Development, January 2015)

- ↑ Enabling POWER 8 advanced features on Linux (de.slideshare.net, 30.06.2016)

- ↑ OpenSSL CHANGES - Changes between 1.0.1l and 1.0.2 (github.com/openssl): Initial support for PowerISA 2.0.7, first implemented in POWER8. This covers AES, SHA256/512 and GHASH. [...]

- ↑ Bug 1276310 - (rhel7-openssl1.0.2) RFE: Need OpenSSL 1.0.2 (bugzilla.redhat.com)

- ↑ Pakiet: openssl w Debianie Stretch (packages.debian.org)

Dodatkowe informacje

- POWER8 (en.wikipedia.org)

Autor: Werner Fischer