Limity przepustowości danych I/O

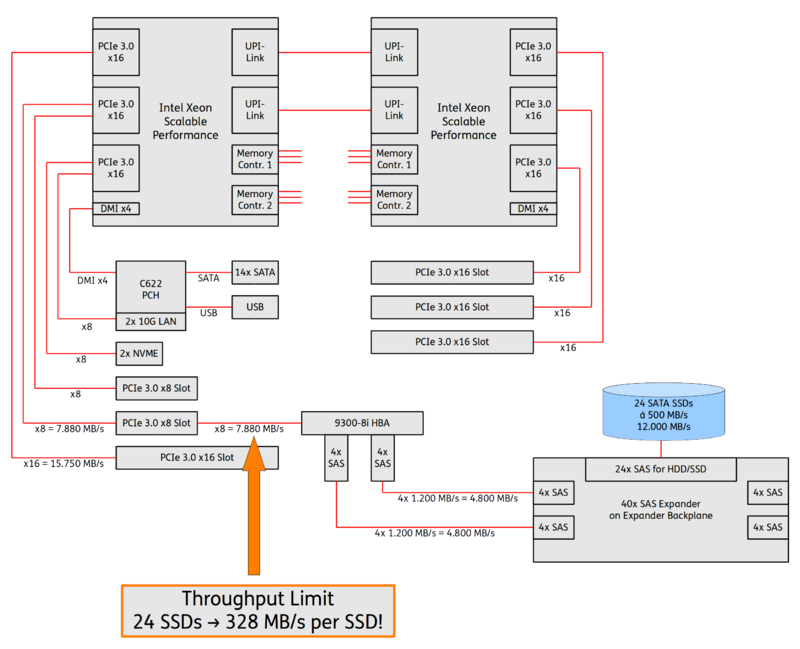

W obliczu licznych optymalizacji wydajności stawia się pytanie o maksymalną możliwą przepustowość danych. W tym krótkim artykule chcemy pokazać, jak zlokalizować wąskie gardło, analizując wszystkie połączenia na ścieżce I/O, wykorzystując do tego schemat płyty głównej Supermicro X11DPi-NT (dla procesorów Intel Xeon Scalable).

Przykładowy serwer z backplanem z chipem SAS Expander

W poniższym przykładzie został wykorzystany serwer z backplenem z chipem expander SAS:

- Backplane z chipem SAS expander jest w tym przykładzie podłączony dwoma 4-portowymi łączami SAS do HBA Broadcom 9300-8i.

- HBA jest podłączone do płyty głównej za pośrednictwem interfejsu PCIe 3.0 x8, który umożliwia przepustowość do 7.880 MB/s. Co w tym przypadku jest granicą maksymalnej możliwej przepustowości danych.

- Backplane z chipem SAS expander oferuje wysoki stopień elastyczności w odniesieniu do ilości nośników danych - w tym przykładzie do 24 dysków SSD lud HDD. Przy takim pełnym obsadzeniu, przepustowość danych jest ograniczona przez wspólne łącze PCI 3.0 x8:

Konsekwencje korzystania z backplane'u z chipem expander

Chip SAS Expander na backplanie znajduje się na ścieżce I/O pomiędzy procesorem a dyskami SSD/HDD. Powoduje on nieznacznie większe opóźnienia i wpływa również na możliwą przepustowość danych każdego nośnika danych. Szczegółowe informacje na ten temat można znaleźć w artykule Wydajność backplane'u z chipem SAS expander.

Przykład z kontrolerem RAID firmy Adaptec

W przypadku korzystania z kontrolera RAID firmy Adaptec, pokazuje arcconf CLI dostępną przepustowość "Host bus speed" (7.880 Mbps):

root@:/usr/home/dg # ./arcconf getconfig 1 | grep -i Host\ Bus Host bus type : PCIe 3.0 Host bus speed : 7880 MBps Host bus link width : 8 bit(s)/link(s)

Dodatkowe informacje

Autor: Werner Fischer