PCIe Reference Clock

Zur Navigation springen

Zur Suche springen

PCIe unterstützt mehrere Clock Modi. Dieser Wiki Artikel gibt einen Übersicht über die unterschiedlichen Modi.

Übersicht

Folgende Clock-Modes sind definiert:[1][2][3]

- Common REFCLK Common Reference Clock

- Data Clocked (nur PCIe 2.0 und 3.0)

- Independent REFCLK (vormals Separate) Reference Clocks

- Separate Reference Clocks with No SSC (SRNS)

- Separate Reference Clocks with Independent SSC[4] (SRIS)

| PCIe Version | Common REFCLK

Rx Architecture (CC) |

Data Clocked

Rx Architecture |

Independent REFCLK

Architecture (IR) | |

|---|---|---|---|---|

| SRNS | SRIS | |||

| PCIe 1.0 | ✔ | - | ? | - |

| PCIe 2.0 | ✔[7][8] | ✔ | ||

| PCIe 3.0 | (x) | |||

| PCIe 4.0 | - | ✔ | ||

| PCIe 5.0 | ||||

| PCIe 6.0 | ||||

Weitere Informationen

- Videos von IDT:

- Videos von Microchip Technology:

- Clocking Architectures in PCI-Express (www.truechip.net, 19.07.2022)

- Intel® 500 Series Chipset Family On-Package PCH Datasheet Volume 1 - Separate Reference Clock with Independent SSC (SRIS) (edc.intel.com) Inclusion of the reference clock in the cable requires an expensive shielding solution to meet EMI requirements. [...] The need for an inexpensive PCIe* cabling solution for PCIe* SSDs requires a cabling form factor that supports non-common clock mode with spread spectrum enabled, such that the reference clock does not need to be part of the signals delivered through the cable. This clock mode requires the components on both sides of a link to tolerate a much higher ppm tolerance of ~5600 ppm compared to the PCIe* Base Specification defined as 600 ppm.

Einzelnachweise

- ↑ Clocking Architectures in PCI-Express (www.truechip.net, 19.07.2022)

- ↑ Verification of SRIS/SRNS Clocking - Whitepaper (PDF) (www.esaindia.com, 19.07.2022)

- ↑ Selecting the Optimum PCI Express Clock Source (PDF) (www.skyworksinc.com, 19.07.2022)

- ↑ Spread Spectrum Clocking (de.wikipedia.org)

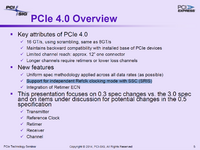

- ↑ PCI Express 4.0 Electrical Previews - Page 5 (pcisig.com, 2014) PCIe 4.0 Overview [...] New features [...] Support for independent Refclk clocking mode with SSC (SRIS) (Bild)

- ↑ PCI Express 4.0 Electrical Previews - Page 20 (pcisig.com, 2014) IR with SSC (SRIS) defined in 3.0 ECN and 4.0 specification (Bild)

- ↑ congatec Application Note - PCI Express Reference Clock Design Considerations (www.congatec.com, 30.09.2020) The Data Clocked Rx architecture is only supported by PCIe 2.0 and 3.0 and is not supported by most chipsets. Therefore, the Data Clocked Rx architecture is usually not recommended.

- ↑ Why does PCIe 5.0 architecture not support an embedded clock? (www.asteralabs.com)

|

Autor: Werner Fischer Werner Fischer arbeitet im Product Management Team von Thomas-Krenn. Er evaluiert dabei neueste Technologien und teilt sein Wissen in Fachartikeln, bei Konferenzen und im Thomas-Krenn Wiki. Bereits 2005 - ein Jahr nach seinem Abschluss des Studiums zu Computer- und Mediensicherheit an der FH Hagenberg - heuerte er beim bayerischen Server-Hersteller an. Als Öffi-Fan nutzt er gerne Bus & Bahn und genießt seinen morgendlichen Spaziergang ins Büro.

|

Das könnte Sie auch interessieren

CHS und LBA Adressierung von Festplatten

SR108 für die Montage in einem Rack vorbereiten

System Event Log auslesen