AMD Genoa(-X) und Bergamo

Genoa(-X) und Bergamo sind Codenamen für Prozessoren der AMD EPYC 9004 Serie. Sie stellen die vierte Generation von Prozessoren mit der sogenannten Zen-Mikroarchitektur dar und sind damit der Nachfolger von Prozessoren der Milan-Serie. Die neue Serie verwendet den neuen SP5 Sockel und ist in 5nm gefertigt.

Im folgenden werden die Neuerungen und technischen Details der neuen Prozessorserie erläutert.

Aufbau

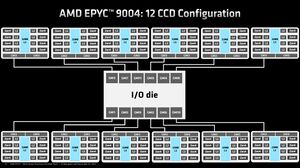

Auch AMD Prozessoren der Zen 4 Architektur setzen auf die bekannten, in Core Complex Die (CCD) organisierten, Chiplets. Möglich sind pro CPU bis zu 12 Chiplets. Jedes Chiplet beinhaltet:

- 8 Kerne

- 1 MB L2-Cache pro Kern

- Shared 32 MB L3-Cache

Alle Chiplets sind mit dem sogenannten I/O-Die verbunden. Neben der Zentralen Schnittstelle für alle Chiplets stellt der I/O-Die zusätzlich folgende Technologien zur Verfügung:

- 12 Memory Controller

- PCIe Gen 5 Controller

- Infinity Fabric Controller

- SATA Controller

- Compute Express Link (CXL) Controller

Er nutzt zudem die AMD Secure Processor Technologie.

Neuheiten

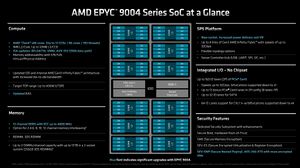

Die 9004 Serie der AMD EPYC Prozessoren bietet Neuerungen in Bezug auf Fertigung, Schnittstellenunterstützung und Befehlssätzen.

Prozessoren der Genoa und Bergamo-Serie sind in 5nm gefertigt. Dadurch ergibt sich ein höherer Basistakt.

Sie unterstützen PCI-Express in der 5. Generation und erhöht damit die Bandbreite für die Anbindung von Datenspeichern auf 32 GT/s pro Lane. Insgesamt können bis zu 128 Lanes bei einer Single-Socket Konfiguration und bis zu 160 Lanes bei einer Dual-Socket Konfiguration genutzt werden.

Die Serie macht außerdem den Sprung zu DDR5 RAM. Über den Memory Controller werden 12 Channel bereitgestellt.

Zu guter letzt gibt es auch Neuerungen im Bereich der Befehlssätze. Mit Genoa und Bergamo werden nun auch VNNI und BFLOAT16 unterstützt.

Milan und Genoa Vergleich

Die folgende Tabelle zeigt die Verbesserungen der auf Zen 4 Architektur basierenden Genoa und Bergamo Prozessorseriegegenüber den Zen 3 AMD Prozessoren mit Codenamen Milan. Für eine Übersicht zum Vergleich der aktuellen Prozessorserie untereinander siehe den Artikel AMD EPYC 9004 Genoa und Bergamo.

| Zen 3 | Zen 4 | Erläuterung | |

|---|---|---|---|

| LDQ | 72 | 88 | Load Queue der Load/Store Unit (LSU)[1] |

| STQ | 64 | 64 | Store Queue der LSU[2] |

| Micro-op cache | 4k ops | 6.75k ops | SRAM Puffer[3] |

| L1 I/D-cache | 32/32k | 32/32k | Layer 1 Instruction/Data-Cache[4] |

| L2 cache | 512k | 1M | Layer 2 Cache |

| L3 cache/core | 4M | 4M | Layer 3 Cache pro Kern |

| L2 TLB | 2k | 3k | Layer 2 Translation Lookaside buffer[5] |

| L2 latency | 12 cycles | 14 cycles | Layer 2 Latenz |

| L3 latency | 46 cycles | 50 cycles | Layer 3 Latenz |

| Issue width (Int + FP/SIMD) | 10+6 | 10+6 | Anzahl der Instruktionen pro Taktzyklus (Integer + Floating Point / Simple Instruction Multiple Data)[6][7] |

| Int reg | 192 | 224 | Integer registration |

| Int scheduler | 96 | 96 | Integer Scheduler |

| FP reg | 160 | 192 | Floating Point registration |

| ROB | 256 | 320 | re-order buffer[8] |

| FADD/FMUL/FMA latency | 3/3/4 cycles | 3/3/4 cycles | Floating Point Addition / Floating Point Mulitplier / Fused Multiply-Add Latenz |

| L1 BTB | 2x 1k | 2x 1.5k | Layer 1 Branch Target Buffer[9] |

| L2 BTB | 2x 6.5k | 2x 7k | Layer 2 Branch Target Buffer |

Weitere Informationen

- AMD EPYC der 4ten Generation: Performance und Energie-Effizienz (TKmag Webinar Aufzeichnung, 24.08.2023)

- AMD EPYC Genoa Gaps Intel Xeon in Stunning Fashion (www.servethehome.com, 10.11.2022)

- AMD EPYC Bergamo is a Fantastically Fresh Take on Cloud Native Compute (www.servethehome.com, 19.07.2023)

Einzelnachweise

- ↑ Load/Store Unit (LSU) (docs.boom-core.org, 05.10.2023)

- ↑ Load/Store Unit (LSU) (docs.boom-core.org, 05.10.2023)

- ↑ Static Random Access Memory (wikipedia.org, 05.10.2023)

- ↑ CPU Cache (wikipedia.org, 05.10.2023)

- ↑ Translation Lookaside Buffer (wikipedia.org, 05.10.2023)

- ↑ Wide Issue (wikipedia.org, 05.10.2023)

- ↑ Flynn's taxonomy (wikipedia.org, 05.10.2023)

- ↑ Re-Order Buffer (wikipedia.org, 05.10.2023)

- ↑ Branch Target Buffer (wikipedia.org, 05.10.2023)

|

Autor: Stefan Bohn Stefan Bohn ist seit 2020 bei der Thomas-Krenn.AG beschäftigt. Ursprünglich als Berater für IT-Lösungen im PreSales beheimatet, wechselte er 2022 zum Product Management. Dort widmet er sich dem Wissenstransfer und treibt dabei auch das Thomas-Krenn Wiki voran. |