Processor P-states and C-states

Intel processors support multiple technologies to optimize the power consumption. In this article, we provide an overview of p-states (optimization of the voltage and CPU frequency during operation) and c-states (optimization of the power consumption if a core does not have to execute any instructions). For information on how to disable these features, see Disable CPU Power Saving Management in BIOS.

P-states

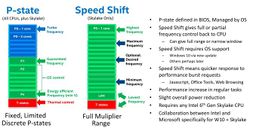

During the execution of code, the operating system and CPU can optimize power consumption through different p-states (performance states). Depending on the requirements, a CPU is operated at different frequencies. P0 is the highest frequency (with the highest voltage).

For Intel processors up to Haswell/Broadwell Architecture, the desired frequency (and thus the voltage) is specified by the operating system by writing the desired values into special processor registers.[1][2]

As of the Skylake architecture, the operating system can leave the control of the P-states to the CPU (Speed Shift Technology, Hardware P-states).[3] With Kaby Lake, these functions have been further optimized.[4]

C-states

Unlike the P-States, which are designed to optimize power consumption during code execution, C-States are used to optimize or reduce power consumption in idle mode (i. e. when no code is executed).

Typical C-states are:[5]

- C0 – Active Mode: Code is executed, in this state the P-States (see above) are also relevant.

- C1 – Auto Halt

- C1E – Auto halt, low frequency, low voltage

- C2 – Temporary state before C3. Memory path open

- C3 – L1/L2 caches flush, clocks off

- C6 – Save core states before shutdown and PLL off

- C7 – C6 + LLC may be flushed

- C8 – C7 + LLC must be flushed

C-States can be distinguished according to core C-states (CC-states), package C-states (PC-states) and logical C-states. In most cases, the operating system sets a specific C-state for a core by executing the MWAIT command.[6]

References

- ↑ Intel Xeon Processor E3-1200 v3 Product Family Datasheet – Volume 1 of 2 4.2.1 Enhanced Intel SpeedStep Technology Key Features: [...] Multiple frequency and voltage points for optimal performance and power efficiency. These operating points are known as P-states. [...] Frequency selection is software controlled by writing to processor MSRs. [...] All active processor cores share the same frequency and voltage. In a multicore processor, the highest frequency P-state requested among all active cores is selected.

- ↑ What exactly is a P-state? (Pt. 1)

- ↑ Intel’s 6th Gen Skylake Unwrapped – CPU Microarchitecture, Gen9 Graphics Core and Speed Shift Hardware P-State (wccftech.com, 18.08.2015)

- ↑ Intel Kaby Lake: 14nm+ und optimiertes Speed Shift steigern Performance (TKmag, 10.03.2017)

- ↑ Intel Xeon Processor E3-1200 v5 Product Family Datasheet - Volume 1 of 2 Chapter 4 Power Management

- ↑ C-states, C-states and even more C-states (software.intel.com, 27.03.2008)

Additional Infomation

- Energy-Efficient Platforms – Considerations for Application Software and Services (www.intel.com, März 2011)

- C-States, P-States, S-States - Energieverwaltung erklärt (www.technikaffe.de, 23.10.2013)

|

Author: Werner Fischer Werner Fischer, working in the Knowledge Transfer team at Thomas-Krenn, completed his studies of Computer and Media Security at FH Hagenberg in Austria. He is a regular speaker at many conferences like LinuxTag, OSMC, OSDC, LinuxCon, and author for various IT magazines. In his spare time he enjoys playing the piano and training for a good result at the annual Linz marathon relay.

|