POWER8

| Hinweis: Bitte beachten Sie, dass dieser Artikel / diese Kategorie sich entweder auf ältere Software/Hardware Komponenten bezieht oder aus sonstigen Gründen nicht mehr gewartet wird. Diese Seite wird nicht mehr aktualisiert und ist rein zu Referenzzwecken noch hier im Archiv abrufbar. |

|---|

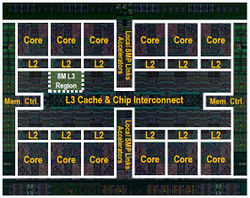

POWER8 CPUs kommen unter anderem in OpenPOWER Servern zum Einsatz. In diesem Artikel zeigen wir einige der Eigenschaften dieser CPUs, wie Anzahl an Cores oder Threads sowie Informationen zu Größe der Caches und Eigenschaften der eingebauten Beschleuniger (Accelerators).

POWER8 CPUs

POWER8 CPUs sind in Varianten mit 4, 6, 8, 10 oder 12 Cores erhältlich.[1] Die folgende Tabelle zeigt Beispiele von 8-Core und 10-Core POWER8 CPUs:[2][3][4]

| Cores | Max. Threads (bei SMT=8) | Frequency (Nominal) | Frequency (Turbo) | TDP (Nominal) | Part Number |

|---|---|---|---|---|---|

| 8 | 64 | 2.328 GHz | 3.026 GHz | 130 W | 00UL867 |

| 8 | 64 | 3.325 GHz | 3.857 GHz | 190 W | 00UL866 |

| 10 | 80 | 2.095 GHz | 2.827 GHz | 130 W | 00UL865 |

| 10 | 80 | 2.926 GHz | 3.492 GHz | 190 W | 00UL864 |

Beispielausgabe lscpu

Das folgende Beispiel zeigt die Ausgabe von lscpu auf einem Produkt nicht mehr verfügbar. Dieser ist mit einer 8-Core CPU mit 190W TDP (Part Number 00UL866) ausgestattet:

tk@ubuntu-16-04:~$ sudo lscpu Architecture: ppc64le Byte Order: Little Endian CPU(s): 64 On-line CPU(s) list: 0-63 Thread(s) per core: 8 Core(s) per socket: 8 Socket(s): 1 NUMA node(s): 1 Model: 2.0 (pvr 004d 0200) Model name: POWER8 (raw), altivec supported CPU max MHz: 3857.0000 CPU min MHz: 2061.0000 L1d cache: 64K L1i cache: 32K L2 cache: 512K L3 cache: 8192K NUMA node0 CPU(s): 0-63

POWER8 CPU Caches

POWER8 basierte Systeme erweitern die Cache-Hierarchie um eine Ebene: einen L4-Cache, der in den jeweiligen Memory Buffer Chips (Centaur) Chips am Mainboard implementiert ist. Die Caches haben dabei folgenden Umfang:[5]

| Cache | Größe | Bandbreite | Gesamtgröße bei einer 8-Core-CPU |

|---|---|---|---|

| L1 Instruction | 32 KB / Core | 256 KB | |

| L1 Data | 64 KB / Core | Four 16 B reads or one 16 B writes per cycle | 512 KB |

| L2 | 512 KB / Core | 64 B reads und 16 B writes per cycle | 4 MB |

| L3 | 8 MB / Core | 32 B reads und 32 B writes per cycle | 64 MB |

| L4 | 16MB / Centaur Chip | z.B. 64 MB bei 4 Centaur Chips |

Detaillierte Informationen zum Cache und Memory Subsystem der POWER8 CPUs gibt es ein einem Beitrag auf researchgate.net.[6]

POWER8 CPU Accelerators

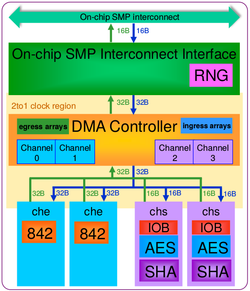

POWER8 CPUs enthalten sogenannte On Chip Accelerators (pro CPU) und In Core Accelerators (pro Core). Mit diesen können bestimmte Aufgaben wie Verschlüsselungs- oder Komprimierungsaufgaben in Hardware beschleunigt werden.[7]

On Chip Accelerators

Der sogenannte Second generation Nest Accelerator complex (NX) Teil einer POWER8 CPU bietet folgende Funktionen:

- Verschlüsselung: Encryption Engine for Symetric Crypto

- Komprimierung: Two 842 compression / decompression engines

- Zufallszahlen: Random Number Generator

Der NX kann auf den gesamten Speicher des POWER8-Systems zugreifen und aus jedem Core heraus zugegriffen werden. Der Zugriff erfolgt dabei über das Linux System, das nativ auf dem POWER8 System läuft (nicht KVM virtualisiert).

In Core Accelerators

Der folgende Beschleuniger ist auf jedem Core implementiert:

- Symetric Crytpo

Er kann auch direkt aus einem Gast-System (z.B. KVM) heraus verwendet werden.

OpenSSL unterstützt ab Version 1.0.2 direkt diesen In-Core-Accelerator.[8] Die folgenden Linux Distributionen enthalten OpenSSL Version >= 1.0.2 und bringen somit für die POWER8-Architektur die Unterstützung dazu mit:

Einzelnachweise

- ↑ POWER8 (en.wikipedia.org)

- ↑ TYAN CPU Support - POWER8 (www.tyan.com)

- ↑ POWER8 CPUs (www.crowdsupply.com)

- ↑ GT75-BP012 FRU Parts Table (www.tyan.com)

- ↑ S812LC Technical Overview and Introduction Table 1-5 POWER8 cache hierarchy (www.redbooks.ibm.com)

- ↑ The cache and memory subsystems of the IBM POWER8 processor (www.researchgate.net, Article in IBM Journal of Research and Development, January 2015)

- ↑ Enabling POWER 8 advanced features on Linux (de.slideshare.net, 30.06.2016)

- ↑ OpenSSL CHANGES - Changes between 1.0.1l and 1.0.2 (github.com/openssl): Initial support for PowerISA 2.0.7, first implemented in POWER8. This covers AES, SHA256/512 and GHASH. [...]

- ↑ Bug 1276310 - (rhel7-openssl1.0.2) RFE: Need OpenSSL 1.0.2 (bugzilla.redhat.com)

- ↑ Paket: openssl in Debian Stretch (packages.debian.org)

Weitere Informationen

- POWER8 (en.wikipedia.org)

|

Autor: Werner Fischer Werner Fischer arbeitet im Product Management Team von Thomas-Krenn. Er evaluiert dabei neueste Technologien und teilt sein Wissen in Fachartikeln, bei Konferenzen und im Thomas-Krenn Wiki. Bereits 2005 - ein Jahr nach seinem Abschluss des Studiums zu Computer- und Mediensicherheit an der FH Hagenberg - heuerte er beim bayerischen Server-Hersteller an. Als Öffi-Fan nutzt er gerne Bus & Bahn und genießt seinen morgendlichen Spaziergang ins Büro.

|